SI/PI/EMC analysis

Signal Integrity

Experience of handling prelayout & postlayout designs/topologies helps customer to first time right designs.

Successfully executed complex Multidrop/Multipoint topologies.

Asserting PCB layer stackup/Layer ordering/PCB materials based on SI results.

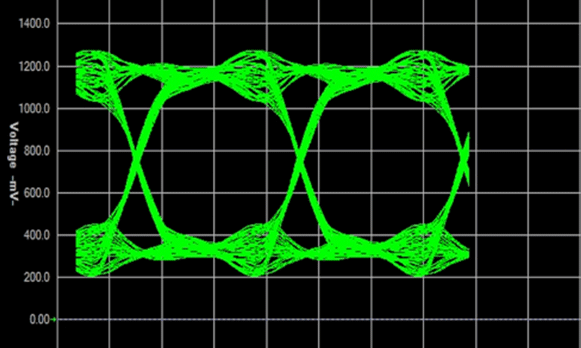

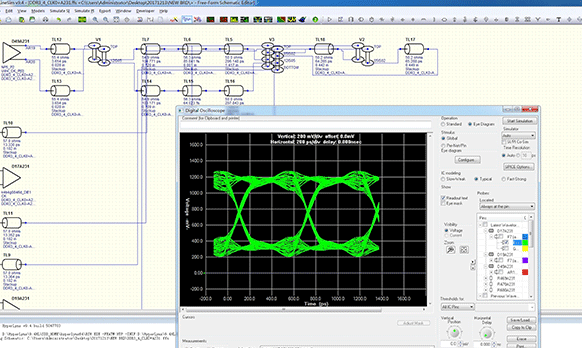

Validating the logic level, Drive strengths, Termination techniques, Thresholds, Over/Under shoot, Propagation Delay, Noise margin etc., Slew Rate, Timing Budget(setup/Hold time), EYE Diagram.、

BER, ISI, Jitter, Loss(IL,RL) analysis.

Cross talk analysis and mitigation methodologies.

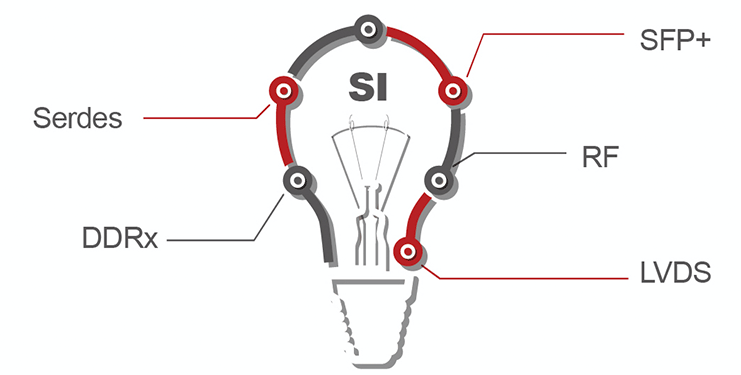

SerDes/DDRx/XAUI/PCIe interfaces.

Handled upto 12.5Gb speed.

SI-Signal Integrity

Signal Integrity

Prelayout & postlayout designs/topologies

BER, ISI, Jitter, Loss(IL,RL) analysis.

Cross talk analysis

Timing Budget(setup/Hold time), EYE Diagram

Complex Multidrop/Multipoint topologies

PI-Power Integrity

Power Integrity

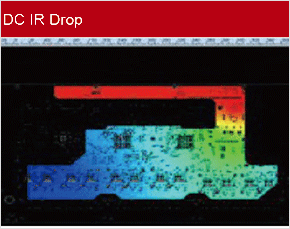

IR/DC Drop analysis

Voltage/Current Density

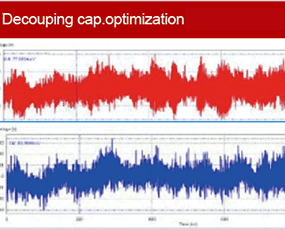

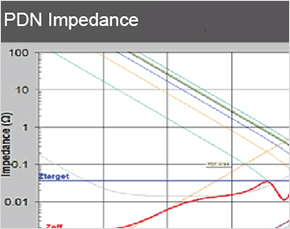

3D plots Decoupling Analysis with Frequency

V/S Impedance plotPlane

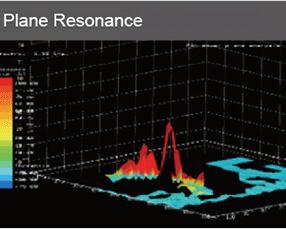

Noise Analysis with 3D plot of plane noise

EMC

EMC Analysis

Frequency V/S dB plot for Different standards

RE/CE analysis

RI/CI analysis

3D Magnetic/Electric & Current density Plots

Noise Analysis with 3D plot of plane noise

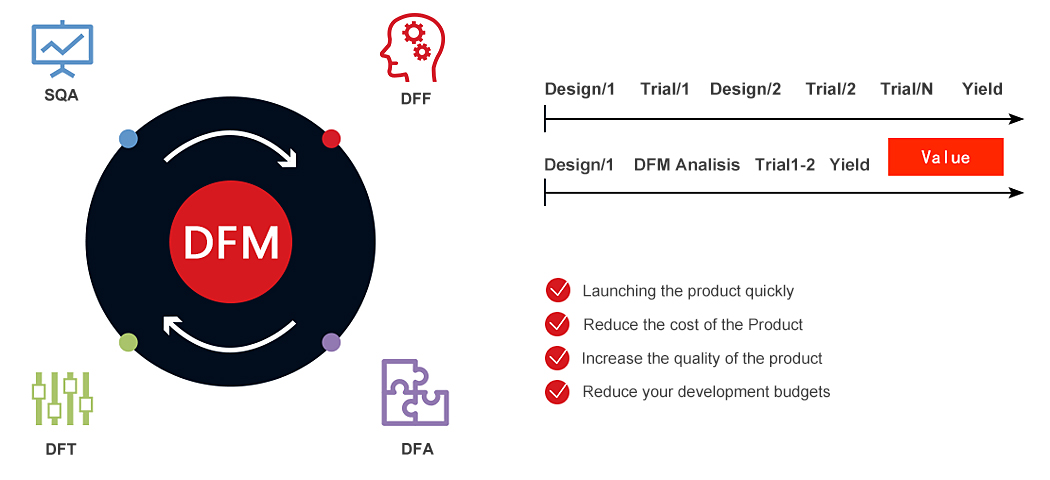

DFM-Design for Manufacture

Design for manufacture

DFM Analysis

DFA Analysis

DFT Analysis

信号Signal Integrity

Experience of handling prelayout & postlayout designs/topologies helps customer to first time right designs.

Successfully executed complex Multidrop/Multipoint topologies.

Asserting PCB layer stackup/Layer ordering/PCB materials based on SI results.

Validating the logic level, Drive strengths, Termination techniques, Thresholds, Over/Under shoot, Propagation Delay, Noise margin etc., Slew Rate, Timing Budget(setup/Hold time), EYE Diagram.

BER, ISI, Jitter, Loss(IL,RL) analysis.

Cross talk analysis and mitigation methodologies.

SerDes/DDRx/XAUI/PCIe interfaces.

Handled up to 12.5Gb speed.

| Analysis Item | |

|---|---|

| Layer | 2-64L |

| Thickness | 0.5-17.5mm |

| Min M | 0.1mm |

| Hole | 3mil |

| HDI | 1+n+1\2+n+2\3+n+3 |

Power Integrity analysis

Design For Fabrication Anaysis

The DFF is a process of optimizing the design data so that it can be the manufactured at least cost without sacrificing the design intent.

DFA Analysis helps you to resolve manufacturability issues, increases reliability,

reduces rework cost and most importantly helps you to meet “TIME TO MARKET”